【発表者】

酒⾒ 悠介 (千葉⼯業⼤学 数理⼯学研究センター 上席研究員)

森野 佳⽣ (九州⼤学 ⼤学院総合理⼯学研究院 准教授)

森江 隆 (九州⼯業⼤学 ⼤学院⽣命体⼯学研究科 特任教授・名誉教授)

細⾒ 岳⽣ (NEC デジタルテクノロジー開発研究所 主幹研究員)

合原 ⼀幸 (東京⼤学 特別教授・名誉教授/東京⼤学国際⾼等研究所ニューロインテリジェンス国際研究機構 副機構⻑/千葉⼯業⼤学 数理⼯学研究センター 主席研究員 (嘱託))

■ 概要

酒⾒悠介 (千葉⼯⼤)、森野佳⽣ (九州⼤)、森江隆 (九⼯⼤)、細⾒岳⽣ (NEC)、合原⼀幸 (東⼤)は、脳の数理モデルであるスパイキングニューラルネットワーク※1を⽤いることで、深層学習の超低消費電⼒ハードウェアである In-memory computing 回路※2を⾼性能化する仕組み「RC-Spike」を考案し、数値シミュレーションでその効果を実証することに成功しました。この成果は、2022 年 5 ⽉ 30 ⽇に査読付き国際学会 IEEE International Symposium on Circuits and Systems (ISCAS2022)で発表されました。

■ 背景

近年、深層学習による⼈⼯知能(AI)の性能向上により、画像認識、翻訳、⾃動運転などの複雑なアプリケーションが実社会で応⽤可能になってきました。しかし、実社会で深層学習を運⽤するにあたっては、認識性能などのアルゴリズム的な性能のみならず、物理的制約を考慮する必要があり、特に消費電⼒は⾮常に重要です。深層学習は⼀般に電⼒消費が⼤きいため、バッテリー容量が限られるスマートフォンやロボットなどのデバイス上で駆動させるのは困難です。そのため、深層学習の電⼒消費を低減することが AI 研究の重要課題となっています。

消費電⼒を低減する最も直接的な⽅法の⼀つは専⽤ハードウェアを作ることです。近年、深層学習⽤のハードウェアの開発が、学術界のみならず産業界でも精⼒的に取り組まれています。数あるハードウェア⽅式の中で、特に⾼い電⼒効率を⽰しているのが In-memory computing (IMC)※2と呼ばれる、アナログ演算回路です。原理は極めて単純で、抵抗に流れる電流を⾜し合わすことで、深層学習のコアの演算である積和演算を⾏います。In-memory computing 回路は深層学習の電⼒効率を⾶躍的に向上させましたが、「既存のアルゴリズムをハードウェアにマッピングする」という⼀般的なトップダウンな発想のもと開発が進んできました。

■ 内容

本研究では、IMC 回路のさらなる⾼性能化を⽬指し、脳のモデルであるスパイキングニューラルネットワーク (SNN) ※1を応⽤しました。SNN を回路化し、知能システムを構築する研究はニューロモルフィックエンジニアリングとして知られており、「回路をニューロンと⾒なし、それらを繋ぎ、ネットワークを構築し、学習させる」というボトムアップ的な発想に基づいています。私たちは、このボトムアップ的な発想をもとに、IMC 回路を再構成することを⽬指しました。

私たちが⾏った再構成は、IMC 回路の構成要素(ニューロン)を単純化し、それをもとにネットワークを構築するということです。この単純化した構成を私たちは RC-Spike と名付けました。

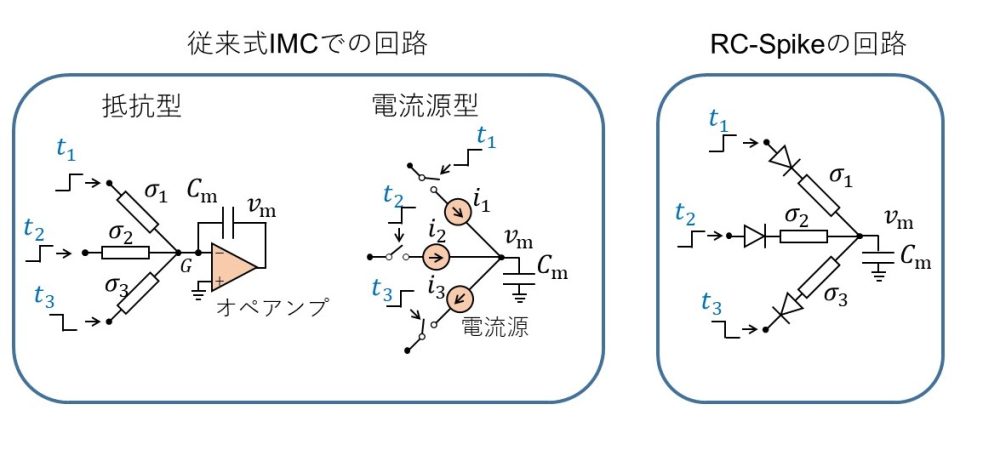

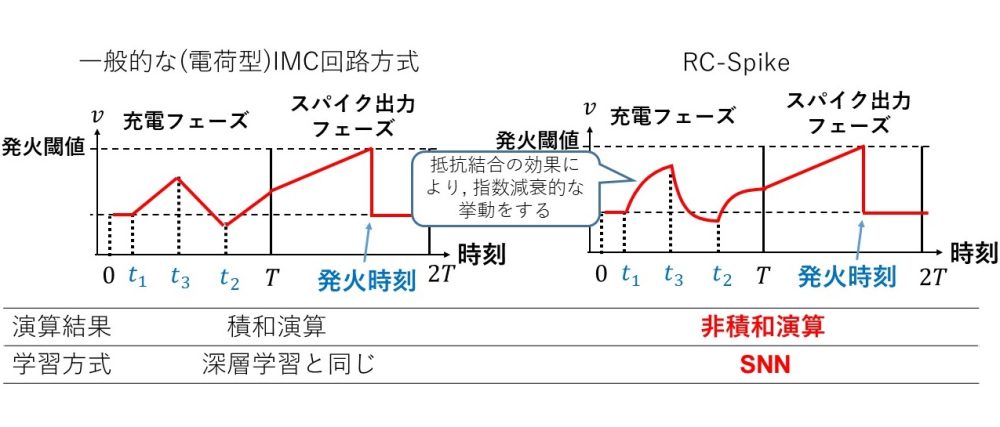

図 1 に従来式 IMC での回路と、RC-Spike の回路を⽐較しています。RC-Spike では、従来式のようなオペアンプや電流源のようなアクティブデバイスが取り除かれていることがわかります。これにより電⼒効率の向上や回路⾯積の縮⼩が可能になります。図2に、従来式 IMC 回路とRC-Spike での動作を⽐較しています。従来式 IMC 回路では、キャパシター電圧の時間発展は区分線形的であり、ニューロンの出⼒は積和演算と同等となります。IMC 回路はこの性質により深層学習の演算が可能になります。⼀⽅で、RC-Spike では、時間発展が指数関数的減衰の特性を持ち、出⼒も積和演算とは異なります。これは、キャパシターに流れ込む電流が、キャパシターの電圧に依存してしまう特性 (抵抗結合効果: 図1)によるものです。そのため、RC-Spike は、⼀般的な深層学習をそのまま演算することはできません。そこで私たちは、RC-Spike を SNNと⾒なし、SNN の学習アルゴリズムを導出することでこの問題を解決しました (学習則の詳細は原論⽂参照)。

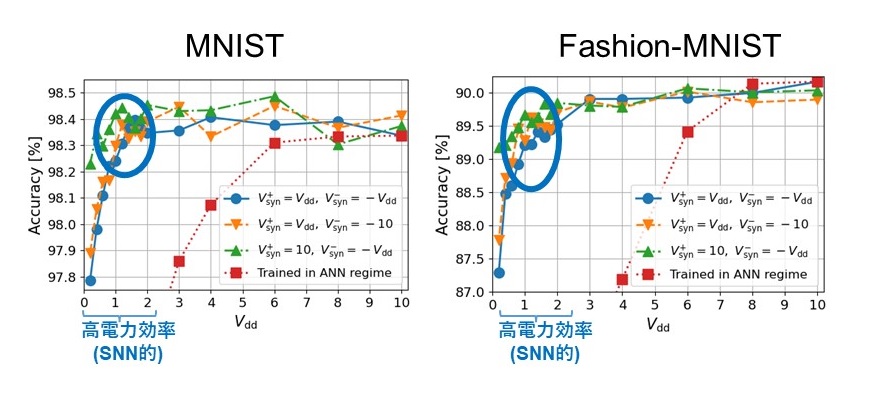

隠れ層が⼆層ある RC-Spike の SNN (784-200-200-10)を標準的ベンチマークである MNISTと Fashion-MNIST で学習させました。RC-Spike は、駆動電圧に相当するパラメータ Vsyn によって、動作モードを連続的に変化させることが可能で、Vsyn が⼩さいほど、電⼒効率が向上しますが、動作が SNN 的(抵抗結合効果が⼤きい)になります。 図 3 に⽰すように、RC-Spikeは、抵抗結合効果が強くなる領域 (Vsyn ~ 1)においても、⼀般的な深層学習と同程度の性能を維持することができています。これらの結果から、RC-Spike によって、認識性能を損なわずに、IMC 回路を簡略化し電⼒効率を⾼めることが可能であると⾔えます。

このように、本研究によって、回路素⼦に着⽬してアルゴリズムを構築していくアナログ回路設計のボトムアップ的アプローチは、実⽤上の⼤きな利点があることを⽰すことができました。また、本研究は、SNN の新たな活⽤⽅法を⽰したという点でも重要です。⼀般的な SNN の回路化を⽬指すニューロモルフィックエンジニアリングでは、SNN のもつ⾮同期性やスパイク通信の特性に着⽬しますが、本研究では SNN の柔軟なモデリング特性に着⽬し応⽤しました。今後、より詳細なアナログ回路の特性を取り込んだアルゴリズムの開発や、回路試作などを通して、重要社会課題である AI の電⼒問題に取り組んでいきます。

※1) スパイキングニューラルネットワーク (SNN)

ニューロン間の情報伝達が 0 または1 の状態で表されるスパイク信号(パルス)で⾏われるニューラルネットワーク。ニューロンはスパイク信号を受け取ると、内部状態である膜電位が変化していき、ある閾値を超えると⾃⾝もスパイク信号を⽣成し、ほかのニューロンへ伝達する。

※2) In-memory computing (IMC)回路

既存のデジタル演算システムは、演算器とメモリが分離した構成をしているが、深層学習のようなデータ中⼼のアルゴリズムでは、それらの間の信号伝送に⼤きな電⼒が必要であり、電⼒効率上のボトルネックとなっていた。In-memory computing は記憶機能のみを有していたメモリセルアレイにアナログ演算機能を持たせることで、このボトルネックを解消し、電⼒効率を⾶躍的に向上させた。情報は抵抗値として保存されており、抵抗に流れる電流 (オームの法則) を⾜し合わせることで (キルヒホッフの法則) 積和演算を実現することができる。本研究では特に、電荷を演算結果とする⽅式 (charge-domain computing)のことを指している。なお、Computing-in-memory (CIM)回路と呼ばれることも多い。

■ 発表会議情報

国際会議名: IEEE International Symposium on Circuits and Systems (ISCAS)

論⽂題⽬: A Spiking Neural Network with Resistively Coupled Synapses Using

Time-to-First-Spike Coding Towards Efficient Charge-Domain Computing

著者: Yusuke Sakemi、Kai Morino、Takashi Morie、Takeo Hosomi、and Kazuyuki Aihara

URL: https://ieeexplore.ieee.org/document/9937662

DOI: 10.1109/ISCAS48785.2022.9937662

発表⽇時: 2022 年 5 ⽉ 30 ⽇

■ 謝辞

本研究の⼀部は、⽇本電気株式会社、JST Moonshot R&D Grant Number JPMJMS2021、AMED under Grant Number JP21dm0307009、セコム科学技術振興財団から助成を受けて⾏われました。

<問い合わせ先>

【本研究内容に関する問い合わせ先】

千葉⼯業⼤学 数理⼯学研究センター 上席研究員

酒⾒ 悠介

【取材・⼤学広報関連に関する問い合わせ先】

千葉⼯業⼤学 ⼊試広報部

⼤橋 慶⼦

■ 添付資料

図 1 従来の IMC と RC-Spike の回路実装(充電フェーズ)の⽐較

従来式 In-memory-computing (IMC)回路では、キャパシタ―に流れ込む電流が膜電位に依存し ないようにオペアンプや電流源などのアクティブデバイスを⽤いる。アクティブデバイスは回路 ⾯積と電⼒が増⼤する⽋点がある。⼀⽅、RC-Spike 回路では、電流が膜電位に依存することを 許容する (抵抗結合効果)。電流の逆流を防ぐダイオードが必要ではあるが、アクティブデバイ スが存在しないため電⼒効率を向上させることができる。

図 2 従来の IMC 回路と RC-Spike の動作⽐

左図は従来型In-memory computing(IMC) の膜電位の時間発展を表し、右図は考案した RC-Spike での膜電位の時間発展を表している。従来型では、充電フェーズで、区分線系な時間 発展をしているが、RC-Spike では、指数関数減衰的な時間発展をしている様⼦がわかる。これ は、抵抗結合による効果によるもの。この結果、RC-Spike では、演算結果が積和演算と異なる ものになるため、SNN として学習する必要がある。

図 3 RC-Spike の学習性能

MNIST データセット、Fashion-MNIST での認識性能を評価した。RC-Spike は、駆動電圧に相当するパラメータ Vsyn によって、動作モードを連続的に変化させることができ、Vsyn が⼩さいほど電⼒効率が向上するが、動作が SNN 的(抵抗結合効果が⼤きい)になる。Vsyn が⼩さい領域 (Vdd~1)においても、⼀般的な深層学習と同程度の性能を維持することができている。