1. 発表者:

上ノ原 誠二(研究当時:東京大学 生産技術研究所 ブレインモルフィックAI社会連携研究部門 特任助教、現在:九州工業大学 大学院生命体工学研究科 人間知能システム工学専攻 特任助教)

合原 一幸 (東京大学 特別教授・名誉教授/東京大学国際高等研究所ニューロインテリジェンス国際研究機構(WPI-IRCN)副機構長)

2. 発表のポイント:

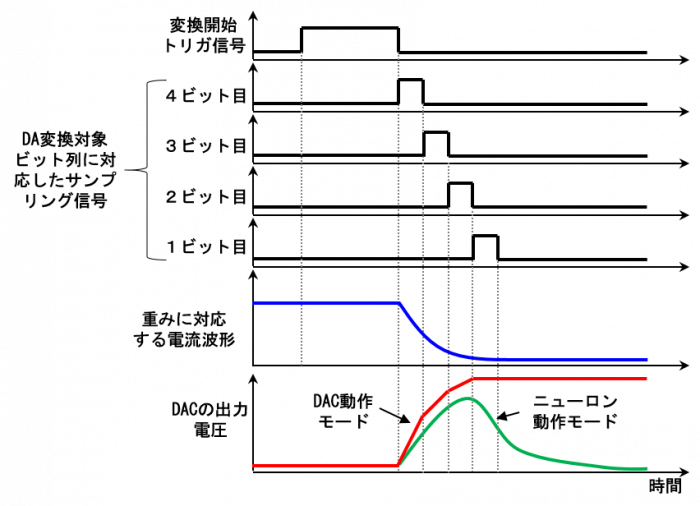

◆デジタル-アナログ(DA)変換を行う際の各ビットの重みを電流波形により時間軸上で実現するDA変換方式を発明した。

◆重みを実現するアナログ回路素子数は変換対象のデジタル信号のビット数に依存しないため、従来のDA変換方式よりも数が少ない。

◆本提案手法は、生理学的に妥当なシナプス応答波形を再現でき、高集積で生体模倣度の高いスパイキングニューラルネットワーク集積回路への応用が期待できる。

3.発表概要:

古典的デジタル計算技術の発展を牽引してきたムーアの法則の終焉を見据え、次世代の新しい計算技術を模索する機運が世界的に高まってきている。その中で、人間の脳を模倣した、スパイキングニューラルネットワーク(SNN)モデルと、その半導体集積回路実装の研究・開発が注目を集めている。

東京大学生産技術研究所の上ノ原誠二特任助教(研究当時、現:九州工業大学 特任助教)と合原一幸東京大学特別教授(東京大学ニューロインテリジェンス国際研究機構 副機構長)は、日本電気株式会社(NEC)と東京大学との社会連携研究部門『ブレインモルフィックAIプロジェクト』の研究において、高集積化が可能で生体模倣度の高いシナプス応答を再現可能なデジタル-アナログ(DA)変換方式を提案した。この方式では、DA変換を行う際の各ビットの重みを電流波形により実現することで(図1参照)、実装面積の大きな回路素子の数を削減した。本提案は、既存デジタルメモリを用いた生体模倣度の高いSNNとアナログ方式による高効率な積和演算(注1)を半導体集積回路上で実現する要素技術として期待できる。

4.発表内容:

<背 景>

人工知能(AI)研究において、高いエネルギー効率で計算を実行するための専用ハードウェアの研究が盛んになっている。AIハードウェア上で演算の大半を占める積和演算はアナログの電流や電圧を用いることで高効率に実行できることが知られている。シナプスの荷重値(注2)をデジタル情報として保持している場合、この積和演算方式の実現にはメモリ上に蓄えられたシナプス荷重値をアナログ信号に変換するDA変換器(DAC)が必要になるが、多値のDACは高集積化に適さないため、この方式が採用されるハードウェアの大半はシナプス荷重値が2値である。特に実際の脳のように非同期で動作するSNNハードウェアでは、単一のDACを時分割処理(注3)により再利用することが困難なため、シナプス回路ごとにDACが必要になる。そのため、チップ上で学習可能なSNNハードウェアの実現にはコンパクトなDACの開発が必要であった。

<内 容>

本研究は、アナログ積和演算方式による高効率で学習機能を持った非同期SNN集積回路を汎用的な半導体製造プロセスで実現するための新しいDACを提案したものである。

通常のDACは、DA変換のために複数の電流源や容量により各ビットの重みを実現しており、変換するビット長の増加に伴い、これらの回路素子数も増加する。回路方式によっては、これらの回路素子数は2のべき乗で増加する。集積回路内では、重みを実現する回路素子は、デジタル回路を構成するトランジスタよりも実装面積がかなり大きい。本研究で提案したDACでは、この重みを時間に伴い指数関数的に変化する電流波形を用いることで時間軸方向に展開し(図1)、大幅な回路部品数の削減を達成した。また、重みを実現するための回路部品数はビット長に依存しない(ただし、デジタル部の回路素子数はビット数に応じて線形に変化する)。

本論文では、提案DACをリーク有り積分発火ニューロン(LIF)(注4)回路の内部状態を更新するシナプス回路の出力段として採用することで、生体模倣度の高いシナプス応答を実現できることを数理的に示した。また、台湾セミコンダクター・マニュファクチャリング(TSMC)(注5)の40nmプロセスで設計したこの回路がLIF動作を実現できることを回路シミュレーションにより示した。

<効 果>

SNNハードウェア実現のためにアナログ回路の利用が有効であることが示されているが、製造バラツキによるパラメータ変動の影響が避けられない。この影響を低減するためにオンチップ学習が有効であり、学習による調整幅を大きく確保するために、多値ビットのシナプス荷重の採用が重要である。本研究で提案したDACを用いることで、製造バラツキに頑健で高効率なオンチップ学習可能なハードウェア開発が期待できる。

本論文では記されていないが、提案DACはTSMC 40nmプロセスで既に試作が完了しており、これにより実際に動作することが確認されている。

5.発表雑誌:

雑誌名:Circuits, Systems, and Signal Processing

論文タイトル:Time-domain digital-to-analog converter for spiking neural network hardware.

著者:Seiji Uenohara *and Kazuyuki Aihara(*:責任著者)

DOI番号:10.1007/s00034-020-01597-2

6.問い合わせ先:

九州工業大学 大学院生命体工学研究科 人間知能システム工学専攻

特任助教 上ノ原 誠二(うえのはら せいじ)

東京大学 特別教授・名誉教授

東京大学国際高等研究所ニューロインテリジェンス国際研究機構(WPI-IRCN)

副機構長 合原 一幸(あいはら かずゆき)

7.用語解説:

注1)積和演算

人工知能モデルの計算では、複数のシナプス(=結合ノード)において、それらが持つ荷重値とそれらへの入力を掛け合わせ(積)、それぞれを足し合わせる(和)演算が大半を占める。

注2)荷重値

人工ニューラルネットワークモデルにおけるシナプス(=結合ノード)が持つ重み定数。この定数を更新することで人工ニューラルネットワークモデルは学習を行う。

注3)時分割処理

1つの装置を用いて2つ以上の処理を時間的にずらして遂行すること。

注4)リーク有り積分発火ニューロン

神経細胞の振る舞いを単純化した数理モデル。他の神経細胞からの入力により、内部状態が変化し、これがしきい値に達すると発火して内部状態が静止状態にリセットされる。入力が無い場合、内部状態はリーク(=漏れ)により時間とともに変化して静止電位に漸近する。竹筒に穴が開いたししおどしのような動作をする神経細胞モデルである。

注5)台湾セミコンダクター・マニュファクチャリング(TSMC)

世界最大の半導体製造メーカ。顧客企業にはアップルなどの有名企業が名を連ねる。

8.添付資料:

図1:提案デジタル-アナログ(DA)変換方式のタイミングチャート。提案方式では、DA変換に必要な各ビットの重みを電流波形で実現している。DA変換対象ビット列の各ビットの1に対応させたサンプリング信号で電流をキャパシタに充電する(図はデジタル値(1111)2を電圧に変換している例)。シナプス回路の出力段としてこれ利用する場合は、変換開始トリガ信号が入力スパイク、DACの出力電圧はニューロンの膜電位に対応する。膜電位に漏れ成分があることにより、生体模倣度の高いシナプス応答が実現される。